# Proposal of a New High Power Insulated Gate Bipolar Transistor

Sachiko Kawaji, Masayasu Ishiko, Katsuhiko Nishiwaki, Toyokazu Ohnishi

## **Abstract**

We propose a new high power insulated gate bipolar transistor with a p<sup>-</sup>/n<sup>+</sup> buffer layer to improve the characteristics of high power IGBTs used in motor control inverters during high voltage operation. The new structure with a p<sup>-</sup> floating layer inserted between n<sup>-</sup> epi and n<sup>+</sup>

buffer layers has a breakdown voltage higher than that of conventional IGBT structures, without increasing the on-voltage. We also demonstrated that with this  $p^-$  floating/ $n^+$  buffer structure, for the first time an IGBT can have performance in the 900V-200A class.

Keywords

HEV (Hybrid Electric Vehicles), Power device, Punch-through type, IGBT (Insulated Gate Bipolar Transistor), High voltage, Floating layer, Electric field

#### 1. Introduction

IGBTs are one of the key components of high-efficiency inverter systems. In the automotive industry, compact high-performance motor-inverter systems are indispensable for advanced hybrid vehicles. We developed low-loss, highly rugged 600V-200A-class planar IGBTs in 1997 and trench IGBTs in 2001 for the first mass production hybrid vehicle. The development of these IGBTs was achieved by adopting state-of-the-art technologies that include local lifetime control by high-energy He<sup>+</sup> ions and a sub-micron trench process. These made possible a low on-voltage of 1.55V at 250A/cm<sup>2</sup> and sufficient short circuit capability.

Recently, new design concepts for improving the characteristics of IGBTs have been proposed. It was shown that the method of carrier accumulation on the emitter side of IGBTs is effective in reducing the on-state voltage. <sup>4, 5)</sup> In addition, the concept of the Field-Stop IGBT also provided effective measures for reducing switching loss <sup>6)</sup> and saving cost. Combination of these new technologies is expected to enable further improvement in IGBTs characteristics.

However, it is known that the performance parameters of IGBTs such as on-state voltage are degraded when the thickness of the n epi layer is increased to increase the device breakdown voltage. For unipolar power devices, it has been reported that the Super Junction (SJ) structure and the Buried Layer (BL) structure have great potential to solve the problem called Si limitation. 7-9) However, little research on IGBTs with such structures has been done. To improve the performance of IGBTs, we have applied the BL concept to an IGBT. More specifically, we investigated an IGBT having a structure with a p floating layer inserted between an n epi layer and an n buffer layer. In this paper, the concept and characteristics of the device are discussed using device simulation. Furthermore, the performance of 900V-200A class IGBTs with a p floating layer/n buffer layer structure is demonstrated for the first time. 10)

#### 2. Device concept and structure

# 2. 1 Basic device structure

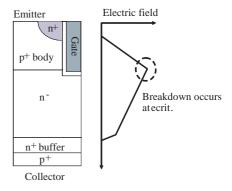

Figure 1 shows cross-sectional views of the

conventional IGBT and its vertical electric field when a high voltage is applied. In general, the breakdown voltage of punch-through type IGBTs (PT-IGBT) depends on the thickness of the n<sup>-</sup> region. Note that a strong electric field peak concentrates at the p<sup>+</sup> body layer/n<sup>-</sup> epi layer interface. This is significant because the breakdown voltage is determined by the electric field strength.

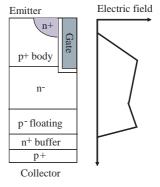

## 2. 2 Novel device structure and concept

**Figure 2** shows cross-sectional views of our proposed device structure and its vertical electric field. Since the floating p layer is inserted in the drift region, two peaks are formed in the electric field; one peak is located at the p body/n epi layer interface, the other one is near the p floating layer/n buffer layer interface. This peak separation results in a reduction in the maximum electric strength of the depletion layer. To clarify the effect

**Fig. 1** Cross-sectional view of device conventional IGBT structure and vertical electric field strength for conventional IGBT.

**Fig. 2** Cross-sectional view of proposed device structure and corresponding vertical electric field strength for proposed structure.

of the p floating layer on the breakdown voltage of our proposed structure, the dependence of the breakdown voltage on the p floating layer thickness was simulated for high and low concentrations of the p floating layer. In the simulation, the total thickness of the n epi layer and the p floating layer was kept at  $70\mu m$ . When the p floating layer thickness is zero, the device structure corresponds to the conventional one.

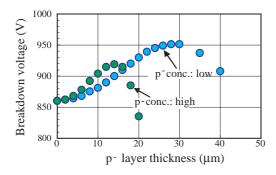

**Figure 3** shows the simulated breakdown voltage as a function of the p<sup>-</sup> floating layer thickness. Compared with that of the conventional structure (Fig. 1), which has only n<sup>-</sup> layer, the breakdown voltage of the proposed structure is increased by 50-100V by inserting a p<sup>-</sup> layer of 15-30μm.

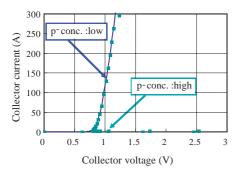

Figure 4 shows the simulated collector currentvoltage characteristics of our proposed device when

**Fig. 3** Simulated breakdown voltages of our proposed device as a function of p<sup>-</sup> floating layer thickness for high and low concentrations of p<sup>-</sup> floating layer. The total thickness of the n<sup>-</sup> and p<sup>-</sup> layers was kept at 70μm.

**Fig. 4** Simulated collector current-voltage characteristics of our proposed device for high and low concentration of the  $p^-$  floating layer. The total thickness of the  $n^-$  and  $p^-$  layers was  $70\mu m$ .

there are high and low concentrations of the p floating layer. The high p layer concentration device exhibited a snap-back effect at the collector voltage of 2.5V, whereas the low concentration device exhibited a smooth curve. Meanwhile the thickness and concentration of the p floating layer did not affect the on-voltage as long as the p impurity concentration was sufficiently lower than the carrier concentration of the p layer in the on-state.

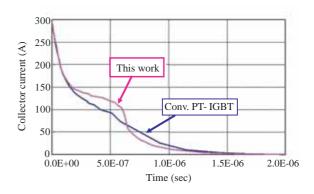

**Figure 5** shows the simulated turn-off curve of the conventional IGBT and the proposed one. The turn-off curve of the proposed structure has a shoulder at 500nsec, whereas the conventional structure has a monotonous decrease. This phenomenon is due to the presence of the p floating layer between the n and the buffer layers, so that tailing starts from the buffer layer side during the turn-off period.

## 3. Experimental results and discussion

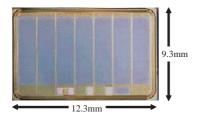

To verify the above simulation results, trench gate PT-IGBTs with a p floating layer were fabricated. The basic structure of the device was the same as a structure reported previously.<sup>3)</sup> **Figure 6** shows a top view of the chip, 12.3 × 9.3mm<sup>2</sup> in size. The rated current was 200A, giving a current density of 250A/cm<sup>2</sup>. A PT-IGBT with the convention structure was also fabricated using the same mask set for comparison.

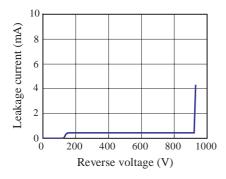

The breakdown voltage of the device with a p

**Fig. 5** Simulated results of the turn-off waveforms curves (proposed and conventional device). Total thickness of  $n^{-}$  and  $p^{-}$  is constant (=70 $\mu$ m) for both. Proposed device has a  $p^{-}$  floating layer (thickness =  $30\mu$ m, concentration =  $10^{14}$ cm<sup>-3</sup>).

floating layer was about 930V, as shown in **Fig. 7**. The breakdown voltage is almost the same as that predicted. The leakage current of the device is; we surmise that this is due to the surface condition of the chip dicing face. Thus, we should be able to suppress this by refining the chip edge treatment and/or the surface termination structure.

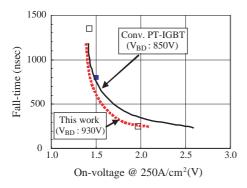

Figure 8 shows the relationship between the on-

**Fig. 6** Top view of fabricated trench gate IGBT.  $(12.3 \times 9.3 \text{mm})$

**Fig. 7** Break down characteristics of the device with a p<sup>-</sup> floating layer on the n<sup>+</sup> buffer.

Fig. 8 Relationship between the on-state voltage and the fall-time for the conventional IGBT and the proposed one. Both simulation (solid and dashed lines) and experimental results (□:proposed structure and ■: conventional) are shown this IGBT.

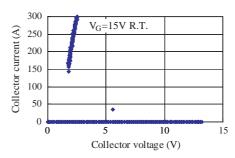

state voltage and the fall-time (trade-off curve) for the conventional IGBT and our proposed IGBT. Both simulation and experimental results are shown in the figure. The on-voltage, fall-time, and breakdown voltage of our proposed device are 1.9V, about 350ns, and 930V, respectively. The onvoltage, fall-time, and breakdown voltage of the conventional type IGBT are, on the other hand, 1.5V, 800ns, and 850V, respectively. These results indicate that p floating layer insertion is effective in improving the trade-off relationship between the onvoltage and the fall-time. Our tentative experiments showed that a collector voltage of 10V or more was necessary to turn the device on as shown in Fig. 9. The on-voltage also exhibited a snap-back immediately after reaching the critical collector voltage. This tendency is similar to that of the simulation with the high concentration p layer in Fig. 4. The phenomenon seems be caused by the thyristor action of the device.

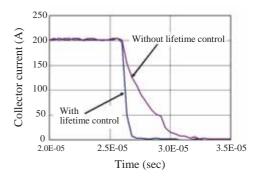

However, the turn-off control by the gate was possible even when the device was without lifetime control as shown in **Fig. 10**. From these results, we

**Fig. 9** Static collector current-voltage characteristics of proposed device.

Fig. 10 Turn-off characteristics of proposed device.

conclude that the conductivity modulation at the nepi region did not take place easily because the actual charge injection into the region in the case where there was a perfloating layer was less than predicted. This is above all probably due to the lifetime values at the perfloating/n<sup>+</sup> buffer region being lower than expected, as a result of which conduction modulation fails to take place in the nepi region unless collector voltage over 10V is applied first. Therefore, we should be able to prevent the above phenomenon by enhancing the efficiency of charge injection from the perfloating layer, which can be achieved by changing the resistivity and thickness of the perfloating and/or nepi floating and/or nepi float

## 4. Conclusion

We proposed a new high power IGBT structure with a p floating layer inserted between the n epi and n buffer. The fabricated device showed improvement of the trade-off relationship between on-voltage and turnoff time. We also demonstrated that with this p floating/n buffer structure, for the first time an IGBT can have performance in the 900V-200A class.

There are still problems that should be solved. However, further improvement of IGBT characteristics based on Si can be expected in combination with our proposed structure and other structures such as CSTBTs (Carrier Stored Trench-Gate Bipolar Transistor), HiGTs (Trench High-Conductivity IGBT) and FS-IGBT (The Field Stop IGBT).

#### References

- Mase, A., Nishiwaki, K. and Kushida, T.:

"Development of an IGBT for Hybrid Vehicles,"

Toyota Tech. Rev., 48-1(1998), 82-87

- 2) Kushida, T., Mase, A., Kawahashi, A. and Ono, K.: "A He-Irradiated IGBT with a Shallow P-Base and Shallow FLRs," Proc. of the 9th ISPSD, (1997), 277-280

- 3) Hamada, K., Kushida, T., Kawahashi, A. and Ishiko, M.: "A 600V 200A Low Loss High Current Density Trench IGBT for Hybrid Vehicle", Proc. of the 13th ISPSD, (2001), 449-452

- Takahashi, H., Haruguchi, H., Hagino, H. and Yamada, T.: "Carrier Stored Trench-Gate Bipolar Transistor (CSTBT) -A Novel Power Device for High Voltage Application-", Proc. of the 8th ISPSD,

- (1996), 349-352

- 5) Oyama, K., Kohno, Y., Sakano, J., Uruno, J., Ishizaka, K., Kasase, D. and Mori, M.: "Novel 600 V Trench High-Conductivity IGBT (Trench HiGT) with Short-Circuit Capability," Proc. of the 13th ISPSD, (2001), 417-420

- 6) Laska, T., Munzer, M., Pfirsch, F., Schaeffer, C. and Schmidt, T.: "The Field Stop IGBT (FS IGBT) A New Power Device Concept with a Great Improvement Potential",: Proc. of the 12th ISPSD, (2000), 355

- 7) Lorenz, L., Deboy, G., Knapp, A. and Marz, M.: "COOLMOSTM A New Milestone in High Voltage Power MOS", Proc. of the 11th ISPSD, (1999), 3-10

- 8) Saito, W., Omura, I., Takano, K., Ogura, T. and Ohnishi, T.: "Ultra Low On-Resistance SBD with P- Buried Floating Layer", Proc. of the 12th ISPSD, (2000), 33-36

- 9) Cezac, N., Morancho, F., Rossel, P., Tranduc, H. and Lavigne, P.: "A New Generation of Power Unipolar Devices", Proc. of the 12th ISPSD, (2000), 69-72

- 10) Ishiko, M., Kawaji, S., Nishiwaki, K. and Ohnishi, T. : "A Novel PT-IGBT with a p /n Buffer Layer", Proc. of the 15th ISPSD, (2003), 341-344 (Report received on Sept. 16, 2004)

# Sachiko Kawaji

Research fields: Power device design for hybrid electric vehicle, Power devices development Academic society: Inst. Electr. Eng. Jpn.

#### Masayasu Ishiko

Research fields: Research and development of IGBTs and power diodes for automobile application Academic society: Inst. Electr. Eng. Jpn., Inst. Electron., Inform. Commun. Eng., Jpn. Soc. Appl. Phys., IEEE

# Katsuhiko Nishiwaki\*

Research fields: Power device design for hybrid electric vehicle

Academic society: Soc. Automot. Eng.

Jpn.

# Toyokazu Ohnishi\*

Research fields: Power device reliability Academic society: Soc. Automot. Eng. Jpn.

\*Toyota Motor Corp.