# **Novel Bi-based High-temperature Solder for Mounting Power Semiconductor Devices**

Yasushi Yamada, Yoshikazu Takaku, Yuji Yagi, Yuji Nishibe, Ikuo Ohnuma, Kiyohito Ishida

## **Abstract**

We have studied a novel high-temperature solder for mounting the power semiconductor devices used in the inverters of hybrid and fuelcell vehicles. The melting point of well-known lead-free solders such as Sn-based alloys is around 220 °C, which is too low to allow their use with high-temperature compound power semiconductor devices such as those based on GaN and SiC. To overcome the brittleness of Bi, we have developed a new Bi-based solder that consists of Bi with CuAlMn particles, the melting point of which is 270 °C. The CuAlMn particles are prepared by a gas-atomizing method, and are then mixed with molten Bi. Mechanical property measurements revealed that the tensile strength of the fabricated solder was almost two times greater

than that of pure Bi. Consequently, joint samples were fabricated using metal plates and their reliabilities were determined by subjecting them to a thermal cycling test. After almost 2000 cycles of -40/200 °C test, neither intermetallic compounds nor cracks were observed at the Cu interface of a sample in which the CTE (Coefficient of Thermal Expansion) was matched. On the other hand, brittle Bi<sub>3</sub>Ni was observed in the Ni interface sample. In addition, although those joint samples using Sn-Cu solder peeled off during the -40/250 °C test, no degradation was observed for those samples using the developed solders. In conclusion, the developed solder seems to offer the qualities needed for use with high-temperature power semiconductor devices.

Keywords

Power semiconductor device, Solder, Lead-free, Joints, Tensile strength, Reliability, Bismuth, Inverter

#### 1. Introduction

Hybrid vehicles and fuel cell vehicles are set to play a vital role in reducing the carbon dioxide emissions produced by automobiles. These vehicles use an inverter that converts DC power to three-phase AC power to control the motor system. This inverter uses power semiconductor devices such as Si-IGBTs and Si-diodes. Miniaturization of the inverter will be essential to increasing the market for these vehicles, but this is a difficult challenge due to the limitations imposed by the operating temperature of the Si semiconductor devices, as the devices generally have an upper operating limit of 150 °C. Next-generation power semiconductor devices based on GaN and SiC will be able to operate at high temperatures in excess of 200 °C. 1,2)

The miniaturization challenge includes semi-conductor packaging technologies such as the mounting materials and processes. If we first consider lead-free solders, the melting point of well-known Sn-based solders<sup>3)</sup> such as Sn-Ag and Sn-Cu is around 220 °C, making it difficult to use these types for high-temperature applications. Research to develop high-temperature lead-free solders<sup>4-9)</sup> with a melting point in excess of 250 °C have not produced good results. In addition, very few reports have discussed joint reliabilities as determined using a thermal cycling test.

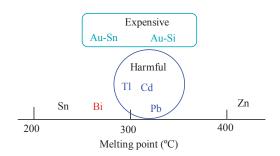

Bi, which has a melting point of 270 °C, is a candidate for use as a solder, as shown in **Fig. 1**. Bi, however, has poor mechanical properties including brittleness and an inferior bonding strength. To overcome these drawbacks, we are proposing a composite solder that is a Bi-based matrix including

**Fig. 1** Overview of melting point of metals in the range from 200 to 450 °C.

dispersed particles of CuAlMn alloy. This paper describes the fabrication process and mechanical properties of the solder, as well as the reliabilities of the joint samples.

# 2. Experimental

# 2. 1 Preparation of the solder

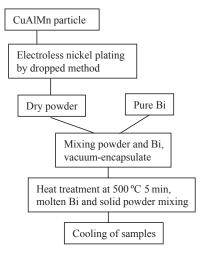

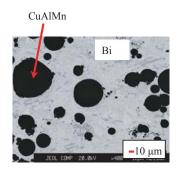

The melting point is controlled by the Bi-based matrix for which relaxation of the thermal stress is expected due to martensite transformation of the CuAlMn particles. We designed a Cu-23at%Al-2at%Mn particle composite. The CuAlMn particles were prepared by a gas atomizing method, and were then coated with electroless Ni plating to improve the Bi wettability of the particles. Then, the coated particles were mixed with molten Bi to produce ingots of solder. The solder fabrication process is shown in **Fig. 2** and the cross-sectional microstructure in **Fig. 3**.

**Fig. 2** Fabrication process of Bi+CuAlMn solder.

**Fig. 3** Cross sectional microstructure of the fabricated Bi+CuAlMn solder.

# 2. 2 Mechanical properties

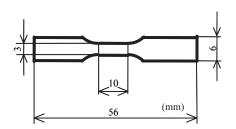

The cast ingots were used to form tensile test specimens<sup>10)</sup> that were almost 10 mm in diameter and 60 mm long. The shape of the specimens is shown in **Fig. 4**. The specimens were machined using an electric discharge machining method and were then annealed at 50 °C for 30 minutes in air to relieve the stress and strain induced by the machining. Specimens were prepared using both a mixture of Bi with CuAlMn particles and pure Bi. The stress-strain properties were measured at -40 °C, 25 °C, 105 °C and 195 °C for Bi with CuAlMn particles, and at 25 °C for the pure Bi.

# 2. 3 Joint samples and reliability

Power semiconductor devices are generally mounted using plain joints, therefore, intermetallic compounds and the effects of fatigue such as cracks and voids play an important role in reliably maintaining the thermal properties of the joint. Firstly, pellet-shaped samples of Bi with CuAlMn were prepared from the ingot, and the pellet size needed to create a joint layer 0.1 mm thick was determined. Joint samples for the reliability test were fabricated from a chip, the composite solder, and a substrate, as shown in **Table 1** and **Fig. 5**.

**Fig. 4** Schematic illustration of the test specimen. Thickness is 2 mm.

Table 1

Joint samples.

The Bi with CuAlMn solder joint was made at around 330 °C (melting point = 270 °C) using an electric hot plate in Ar gas atmosphere. As part of this process, the chip was slightly agitated to promote the formation of a dense solder joint, because the solder exhibits relatively poor wettability. The chips used were Si/Ni [4] or Cu/FeNi/Cu [4], which correspond to the semiconductor device. The substrate was Ni/Al/AlN/Al/Ni [4], Cu/FeNi/Cu [4], or Cu [17] that correspond to the insulated substrate, where the values in [ ] are the CTE (Coefficient of Thermal Expansion, ppm/K). The chips were 0.4 mm thick, and the substrate was 2 mm including interface layers. The interfaces, together with the chip and substrate thicknesses, are also listed in Table 1.

In addition, joint samples using typical Pb-free solder such as Sn-0.7Cu were also prepared for reference. The melting point of this solder is 227 °C, so the joints made with the solder were processed at 280 °C.

Before the reliability tests, the joint samples made using Bi with CuAlMn were observed using an Xray transmission method. Then, the reliabilities were examined subjecting the samples to thermal cycling tests in air. The duration of the tests was 40 minutes, with the minimum temperature of -40 °C and the maximum temperature of 200 °C being held for 20 minutes each, including the transient times (almost 5 minutes). This is abbreviated to -40/200 °C in the following section. The tests were performed continuously for almost 2000 cycles. In addition, -40 and 250 °C tests were also performed. The reliabilities of the joint samples were evaluated by cross sectional microstructure examination using a scanning electron microscope, in terms of intermetallic compounds, cracks, and voids in the

| Matching of CTE | (A) Chip      |                |                                   | (B) Substrate          |                |                                   |

|-----------------|---------------|----------------|-----------------------------------|------------------------|----------------|-----------------------------------|

|                 | Structure     | CTE<br>(ppm/K) | Thickness of interface layer (µm) | Structure              | CTE<br>(ppm/K) | Thickness of interface layer (µm) |

| Mismatched      | Cu/FeNi/Cu    | 4              | 40                                | Cu                     | 17             | 2000                              |

| Matched         | Cu/FeNi/Cu    | 4              | 40                                | Cu/FeNi/Cu             | 4              | 200                               |

| Matched         | Si/ <b>Ni</b> | 4              | 0.7                               | Ni/AlAlN/Al/ <b>Ni</b> | 4              | 5                                 |

Bold: Interface layer

**Fig. 5** Illustration of a joint sample.

solder layers.

#### 3. Results and discussion

# 3. 1 Mechanical properties

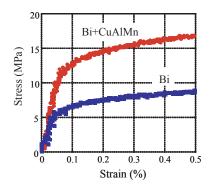

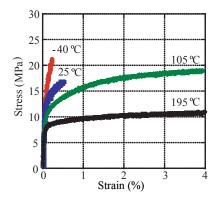

The stress-strain properties of the fabricated specimens are shown in **Fig. 6**. Unsurprisingly, it was found that the tensile strength of the fabricated solders was much better than that of pure Bi. In addition, the mechanical properties were found to strongly depend on the temperature, as shown in **Fig. 7**. Very small, brittle-like fractures were observed at -40 °C and 25 °C, while large strains were observed at 105 °C and 195 °C. In addition, the tensile strength remained at around 10 MPa at 195 °C, indicating that the solder itself exhibits sufficient strength at around 200 °C.

## 3. 2 Joint reliability

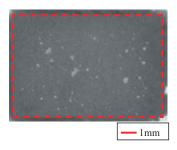

Before the reliability test, the fabricated joint samples were observed by an X-ray transmission

**Fig. 6** Stress and strain curve of solders comparison between Bi and Bi+CuAlMn solder at 25 °C.

**Fig. 7** Temperature dependency of stress and strain properties of Bi+CuAlMn solder.

method. An X-ray photograph of joint between the Si/Ni chip and Ni/Al/AlN/Al/Ni substrate is shown in **Fig. 8**. It can be seen that there are few serious voids and cracks.

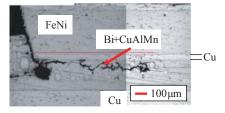

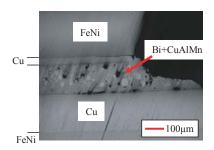

Then, the joint reliabilities were evaluated after the thermal cycling test. Some cracks in the solder layer were observed after 200 cycles of the -40/105 °C test with the CTE-mismatched samples between a Cu/FeNi/Cu chip and Cu substrate, as shown in Fig. 9. The number of cycles and the temperature difference are relatively low, although it does seem that considerable thermal stress/strain was applied the joint layer due to the large mismatch in the CTE of the chip and that of the substrate. In this sample, no intermetallic compounds and cracks are observed between the solder and Cu layer. We believe that the CuAlMn particles in the solder prevent the cracks from growing. On the other hand, we found that there is no compound phase or fatigue in the CTEmatched samples between a Cu/FeNi/Cu chip (Cu interface) and Cu/FeNi/Cu substrate (Cu interface) after 1983 cycles of the -40/200 °C test, as shown in Fig. 10.

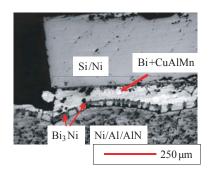

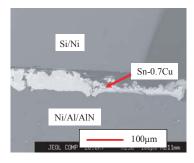

The reliability of the joint samples between Si/Ni

**Fig. 8** X-ray photograph of a joint sample.

**Fig. 9** Cross sectional view of joint samples of Cu/FeNi/Cu chip and Cu substrate after thermal cycling test of -40/105 °C, 200 cycles.

(Ni interface, which was deposited by sputtering) and Ni/Al/AlN/Al/Ni (Ni interface, which was plated) is very different from the results obtained for the Cu interface. A certain amount of intermetallic compounds such as Bi<sub>3</sub>Ni was found after 1944 cycles of the -40/200 °C test, as shown in Fig. 11. The Bi<sub>3</sub>Ni seems to invade the interface Ni layer of the chip and some small cracks in the solder layer were observed. While the maximum temperature (200 °C) of the thermal cycling test is lower than the melting point of the fabricated solder and interface metal, a somewhat active solid-state chemical interaction between Bi and Ni seems to occur at 200 °C. The Bi<sub>3</sub>Ni is very brittle, therefore the joint samples incorporating it do not exhibit sufficient reliability. So, after almost 2000 cycles of the -40/200 °C thermal cycling test, only the Cu interface and CTE-matched samples exhibited a reliable joint.

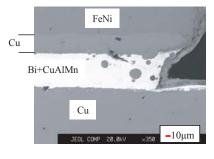

Moreover, no cracks or damage were observed after 200 cycles at -40/250 °C, as shown in **Fig. 12**.

**Fig. 10** Cross sectional view of joint samples of Cu/FeNi/Cu chip and Cu/FeNi/Cu substrate after thermal cycling test of -40/200 °C, 1983 cycles.

**Fig. 11** Cross sectional view of joint samples of Si/Ni chip and Ni/Al/AlN substrate after thermal cycling test of -40/200 °C, 1944 cycles.

The joint samples using conventional Sn-0.7Cu solder melted and peeled off during the test, as shown in Fig. 13.

#### 4. Conclusion

A newly fabricated composite high temperature solder based on Bi with CuAlMn was developed. This solder exhibits a mechanical strength that is almost two times higher than pure Bi. It was found that the CTE-matched samples joined by the solder exhibit excellent reliability when subjected to a thermal cycling test over 200 °C. Consequently, this solder is a candidate for forming the joints between power semiconductor device and an insulated substrate using CTE-matched structure. This should enable the development of a compact inverter using high-temperature GaN or SiC power semiconductor devices.

**Fig. 12** Cross sectional view of joint samples of Cu/FeNi/Cu chip and Cu/FeNi/Cu substrate after thermal cycling test of -40/250 °C, 200 cycles.

**Fig. 13** Cross sectional view of joint samples using conventional Sn-0.7Cu after thermal cycling test of -40/250 °C, 200 cycles.

# Acknowledgements

The authors thank Toyota Motor Corp. for their experimental support. This research was carried out in cooperation with Dr. H. Takao, Dr. H. Tadano, and Mr. A. Yamada of Toyota central R&D Labs.

#### References

- Ueda, H., et al.: "High Current Operation of GaN Power HEMTS", Proc. of 17th Int. Symp. on Power Semiconductor Devices & IC's, (2005), 311

- Asano, K., et al.: "Temperature Dependence of Onstate Characteristics, and Switching Characteristics of 5 kV Class 4H-SiC SEJFET", IEEJ Trans. IA, 125-2(2005), 147

- 3) Nishimura, Y., et al.: "All Lead Free IGBT Module with Excellent Reliability", Proc. of 17th Int. Symp. on Power Semiconductor Devices & IC's, (2005), 79

- Kim, S. S., et al.: "Microstructural Evolution of Joint Interface between Eutectic 80Au-20Sn Solder and UBM", Mater. Trans., 46-11(2005), 2400

- 5) Lee, J. E., et al.: "Interfacial Properties of Zn-Sn Alloys as High Temperature Lead-Free Solder on Cu Substrate", Mater. Trans., **46**-11(2005), 2413

- Shimizu, T., et al.: "Zn-Al-Mg-Ga Alloys as Pb-free Solder for Die-attaching Use", 5th Symp. on Microjoining and Assembly Technology in Electronics, (in Japanese), Feb. 4-5 (1999), 305

- 7) Rettenmayr, M., et al.: "Zn-Al Based Alloys as Pb-Free Solders for Die-Attach", J. Electronic Mater., **31**-4(2002), 278

- 8) Nakano, K., et al.: "Development of Bi-Based Lead-Free Solder Paste", 10th Symp. on Microjoining and Assembly Technology in Electronics, (in Japanese), Feb. 5-6 (2004), 111

- Lalena, J. N., et al.: "Experimental Investigation of Ge-Doped Bi-11Ag as a New Pb-Free Solder Alloy for Power Die Attachment", J. Electronic Mater., 31-11(2002), 1244

- 10) Takao, H., et al.: "Mechanical Properties and Solder Joint Reliability of Low-Melting Sn-Bi-Cu Lead Free Solder Alloy", R&D Rev. of Toyota CRDL, 39-2 (2004), 49

(Report received on Mar. 16, 2006)

#### Yasushi Yamada

Research fields: Electronic materials,

Power electronics

Academic degree: Dr. Eng.

Academic society: Inst. Electr. Eng. Jpn.,

Appl. Phys. Jpn., Inst. Electron.

Packag., Soc. Automot. Eng. Jpn.

#### Yoshikazu Takaku\*

Research fields: Material design, Phase equilibria, Phase transformation,

Lead free solder

Academic degree: Dr. Eng.

Academic society : Jpn. Inst. Metals

# Yuji Yagi

Research fields: Power module design,

Thermal stress simulation

Academic society: Jpn. Soc. Mech. Eng.

#### Yuii Nishibe

Research fields: Power electronics simulation, Power device packaging

Academic degree : Dr. Eng.

Academic society: Inst. Electr. Eng. Jpn. Awards: R&D 100 Award, 2001

## Ikuo Ohnuma\*

Research fields: Computational microstructure design of iron-base alloys, Solder materials, etc.

Academic degree: Dr. Eng.

Academic society: Jpn. Inst. Metals, Iron and Steel Inst. Jpn.

## Kiyohito Ishida\*

Research fields: Microstructure science,

Phase equilibria, Phase

transformation, Material design

Academic degree: Dr. Eng.

Academic society: ASM (USA), TMS (USA), MRS (USA), Jpn. Inst. Metals, Iron and Steel Inst. Jpn., Inst. Light Metals Jpn., Jpn. Inst. Electron. Packag.

Awards: Tanigawa & Harris Award, Jpn. Inst. Metals, 2002 The Best Paper Award, Jpn. Copper and Brass Res. Assoc., 2005

\*Tohoku Univ.