# アナ/ディジ混載IC用の故障モデルと故障シミュ レーション

中條直也,手嶋茂晴

A Voltage Stuck-at Fault Model and Fault Simulation for Mixed-Signal ICs

Naoya Chujo, Shigeharu Teshima

# 要旨

アナ/ディジ混載IC用機能テストを行うテストパターン作成を支援するため,新しい故障モデル"電圧値の縮退故障モデル"と高速な故障シミュレーションの手法を提案する。

対象回路では増幅器などのアナログ機能ブロックがシミュレーションの単位となる基本素子として扱われる。これらのアナログ機能ブロックは入力インピーダンス無限大,出力インピーダンス0としてモデル化される。これらのアナログ機能ブロックの入出力端子に,その電圧レベルが一定値に固定するという,電圧値の縮退故障モデルを提案する。この故障モデルの妥当性を調べるため,数種類のバイポー

ラ回路を例題として故障解析を行った。仮定した オープンショート故障の50%程度がこの故障モデル でカバーできることがわかった。

また,この故障モデルに基づいた故障シミュレーションのアルゴリズムを提案する。提案する故障シミュレーションはイベントドリブン方式で高速な実行が可能である。このアルゴリズムはディジタル回路用故障シミュレーションをアナ/ディジ混載回路用に拡張したものである。試作したシミュレータは従来の回路シミュレーションに基づく故障シミュレーションに比べて50倍以上高速なシミュレーションが可能であることが分かった。

#### Abstract

This paper deals with the problems involved in testing large mixed-signal ICs. To assist in generating test patterns of large mixed-signal circuits for functional tests, a fault model "voltage stuck-at fault" and a fast fault simulation algorithm are proposed.

In this voltage stuck-at fault model, a signal line sticks to a constant voltage level. Under the assumption that the blocks in a circuit are identically designed as current-independent, i.e. their input impedance is regarded as infinite and their output impedance as zero. To verify the validity of this fault model, fault analysis was applied to several bipolar ICs. The analysis of open and short faults between terminals of transistors and

resistors shows that this fault model has sufficient coverage (more than 50% of the faults) to test mixed-signal circuits.

Based on this fault model, a fault simulation algorithm has been designed. The fault simulation is realized by an event driven method and a concurrent method and detects voltage stuck-at faults. These methods are essential for digital fault simulation and are extremely effective to high speed simulation. Actually, a fault simulator was implemented, and some test circuits were simulated. The simulator was found to be more than 50 times faster than the conventional one which was based on the circuit simulation.

キーワード

IC LSI, 試験, CAD, 故障, モデル, シミュレーション, システム化, アナ/ディジ

# 1. はじめに

ASICの発展に伴いアナ/ディジ混載ICの開発が増加している。多くはセンサからのアナログ信号を処理しアクチュエータを駆動させるような制御用の組み込みICとして使用されている。

一方,従来のテスト用CADシステムは,ディジタル回路を中心に研究開発されてきた。アナログ回路やアナ/ディジ回路に対しては,故障モデルやテスト手法がいろいろ提案されているが1-10)一般的なものは存在しない。パラメータを変化させ故障原因を推定する手法3),回路を線形システムで近似して扱う手法4-6)などが提案されている。また,最近,電流テストを用いる手法10)などが提案されている。A/Dコンバータに関しては,アナログ回路とディジタル回路を独立に扱うテスト生成手法7)が提案されている。

しかし、これらの手法は小規模のアナログ回路や特定のアナ/ディジ回路を主な対象としており、大規模な回路に対しては有効とはいえない。本報告では、大規模なディジタル回路を含むアナ/ディジ回路に対しても適用できる故障シミュレーションの手法を提案する120。提案する手法は、ディジタル回路での故障シミュレーション手法を、アナ/ディジ回路にも適用できるように拡張したものである。適用可能なアナログ回路は限定を受けるが、高速な故障シミュレーションが期待できる。

本報告では,まず電圧値を入出力とするシミュレーション用の機能モデルについて2.1節で説明する。次に故障モデルについて2.2節で説明する。次に2.3節で,故障モデルの妥当性について調べるため,バイポーラ回路を例題として故障解析を行った結果を説明する。次に3章で簡単な例題を用いて故障シミュレーションを説明する。最後に考察とまとめを述べる。

# 2. モデル

ここでは,シミュレーションのための機能モデルと故障モデルについて述べる。

#### 2.1 機能モデル

シミュレーションの単位となる回路はアナログ機

能ブロックとする。アナログ機能ブロックは,入力インピーダンス無限大,出力インピーダンス0の理想素子としてモデル化可能なものに限定する。アナログ機能ブロックの機能は直流電圧値によって決定されるものとする。これはディジタル回路における論理ゲートの機能を連続電圧値に拡張したものである。シミュレーションの単位となる回路の機能は区分線形関係で表現される。即ち電圧のI/O関係を,区間ごとに線形関数または定数によって表現する。ここでは,DC的な機能のみを対象としており,周波数応答や遅延については扱わない。

想定しているアナログ機能ブロックは,

- 増幅器

- ・コンパレータ

- アナログスイッチ

- 定電圧源

などである。

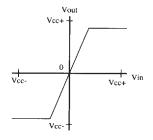

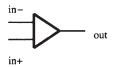

例えば, 増幅器の機能は, Fig. 1のように表現される。

このモデルでに扱うことのできないアナログ機 能ブロックは,

- 単体素子(トランジスタ,抵抗,コンデンサ)

- トランス

- 定雷流源

などである。

# 2.2 故障モデル

前節で述べたアナログ機能ブロックに対して故 障を次のように定義する。

故障:アナログ機能ブロックの一つの信号線の電圧 値が,ある一定値に固定される単一縮退故障。

Fig. 1 Functional model of an amplifier.

この故障モデルによれば,例えばコンパレータのような回路はアナログ機能ブロックとして扱われ,故障としてその入出力に電圧値の縮退故障が仮定される。この故障モデルではアナログ機能ブロックの入出力信号の故障だけを扱う。

# 2.3 バイポーラ回路の故障解析

この故障モデルの妥当性について調べるため,故障解析を行った。解析対象はシミュレーションの単位として扱われるアナログ回路ブロックである。

これらのアナログ回路内部のトランジスタ,ダイオード,抵抗にオープンおよびショート故障を 仮定し,それらが前節で述べた電圧値の縮退故障 という故障モデルとして,どの程度カバーできる かどうかを検証した。

回路としては,バイポーラのアナログ回路を対象とした。バイポーラ回路は,出力インピーダンスが低くドライブ能力が高い,特性の優れたオペアンプが作りやすい,などの特徴を持ちアナ/ディジ混載ICにも搭載される。

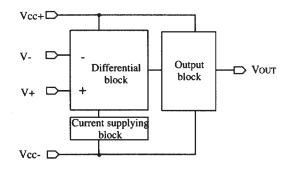

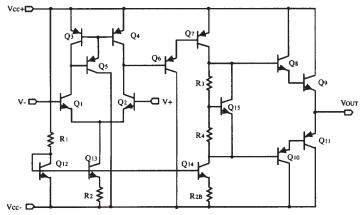

具体的には,オペアンプ<sup>11)</sup>の故障が,縮退故障としてカバーできるか次のように調べた。この回路をFig. 2に示す。

- 回路内部の全トランジスタ,ダイオード,抵抗にオープン,ショートの故障を仮定した

- この回路を電源部,定電流部,差動部,出力

部の4つの部分に分けて回路シミュレータ SPICEのDC解析機能を使用して検証を行った。 Fig. 3に回路ブロックを示す。

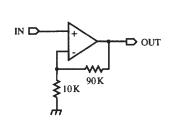

・比較動作を行わせるパターンを入力した。 また, Fig. 4に示すように,同じオペアンプで10 倍の非反転増幅器を構成して故障解析を行った。

解析結果をTable 1, 2に示す。判断としては,出力信号線において故障時の電圧振幅が正常時の20%以下になる場合を,故障モデルで述べた故障に相当するものとした。また,電圧値異常として出力信号線において電圧が電圧振幅の10%以上変化した場合,電源ショートとして電源電流が1A以上となる場合,などをその他の異常とした。

回路例による違いを調べるため,他のオペアン

Fig. 3 Functional blocks of opamp1.

Fig. 2 Schematics of an operational amplifier: opamp1.

Fig. 4 An example of non-invertive amplifier.

プ(opamp2)についても同様に比較器,非反転増幅器を構成し,故障解析を行った。また別の比較器2種(cprt1,cprt2)についても,故障解析を行った。解析結果をTable 3に示す。

さらに,バイポーラのディジタル回路素子(インバータ inv,ヒステリシス付きバッファ bufh)も参考のため調べた。解析結果をTable 4に示す。

Table 1, 2, 3, 4から, 今回の回路例での故障解析の結果をまとめると, 次のようなことが言える。

オープン,ショート故障のうち,縮退故障と

- して平均50.3% 最低38.0% 最高65.3%の割合で カバーできた。

- オペアンプを比較器,増幅器回路など構成を換 えてもこれらの検出率はだいたい同じであった。

- これらのことから、これらのオペアンプ、コンパレータ等の回路ブロックから構成される回路であれば、提案する故障モデルでテストを行うことは意味があると考えられる。

ただし,提案した故障モデルでは基本的に次の ような故障はカバーできない。それらに対しては

| T 11 4  | TD1 1.     | C C 1.   |          |         |             |

|---------|------------|----------|----------|---------|-------------|

| Lable 1 | The result | of fault | analysis | 1151110 | comparator. |

|         |            |          |          |         |             |

|                                 | Total | Differential block | Output<br>block | Current supplying block |

|---------------------------------|-------|--------------------|-----------------|-------------------------|

| Injected faults                 | 100   | 42                 | 34              | 24                      |

| Voltage stuck-at faults         | 44    | 23                 | 8               | 13                      |

| Other faults Irregular voltages | 74    | 36                 | 17              | 19                      |

| Irregular currents              | 14    | 8                  | 3               | 3                       |

Table 2 The result of fault analysis using non-invertive amplifier.

|                                 | Total | Differential block | Output<br>block | Current supplying block |

|---------------------------------|-------|--------------------|-----------------|-------------------------|

| Injected faults                 | 100   | 42                 | 34              | 24                      |

| Voltage stuck-at faults         | 38    | 24                 | 8               | 6                       |

| Other faults Irregular voltages | 69    | 37                 | 16              | 16                      |

| Irregular currents              | 11    | 4                  | 4               | 3                       |

Table 3 The result of fault analysis using other circuits.

|                         | opamp2 (cprt) | opamp2 (amp) | cprt1       | cprt2       |

|-------------------------|---------------|--------------|-------------|-------------|

| Injected faults         | 208           | 208          | 182         | 196         |

| Voltage stuck-at faults | 99 (47.5%)    | 105 (50.4%)  | 119 (65.3%) | 111 (56.6%) |

| Other faults            |               |              |             |             |

| Irregular voltages      | 126           | 130          | 149         | 138         |

| Irregular currents      | 18            | 17           | 20          | 25          |

別のテストを考える必要がある。

- 電流値が異常となるが、回路動作は正常な場合 定電流源の電流制限用抵抗のショート故障など。 電源ショートのように過電流の場合は検出可 能であるが、そうでない場合は、電圧故障モ デルでは正常値との違いが検出できない。

- 異常検出用の回路の故障や保護用の回路の故障 これらの異常検出回路の故障検査には,本来, 専用のテスト設計が必要である。

また入出力部では保護用に抵抗が入れられる ことが多いが,これらがショートしても通常 動作に影響はないため,正常値との違いが検 出できない。

# 3. 故障シミュレーション

# 3.1 故障シミュレーションのアルゴリズム

提案した電圧値の縮退故障モデルを用いることにより、故障シミュレーションを効率的に行うことができる。

各信号線で定義される電圧値の縮退故障は,回路内のディジタルおよびアナログ素子を通過して,出力素子に向かって伝搬される。最終的に出力素子において検出可能な故障として検出される。

機能モデルと故障モデルの節で定義した仮定に従って,故障シミュレーションはディジタル回路の場合と同様に回路内の各ブロックにおける故障伝搬を行うことにより実現される。

我々の提案するアルゴリズムでは,各信号線における故障は(信号線名 故障電圧範囲 影響電圧範囲)の3つの要素で表現する。

故障信号線: 故障を仮定している信号線名。

Table 4 The result of fault analysis using digital circuits.

|                                 | inv | bufh |

|---------------------------------|-----|------|

| Injected faults                 | 54  | 112  |

| Voltage stuck-at faults         | 40  | 60   |

| Other faults Irregular voltages | 46  | 103  |

| Irregular currents              | 4   | 6    |

故障電圧範囲:故障信号線で,固定される電圧範囲[f,f,f]。

故障信号線は,この範囲内の特定の電圧値に縮退(固定)している。この電圧範囲は,素子の区分線形な領域に含まれるものする。この範囲 $[f_i,f_u]$ は,故障した信号線が $f_i$ から $f_u$ に固定することを示している。

影響電圧範囲:故障信号線が故障電圧内の一定値に電圧が固定された時,観測信号線がとり得る電圧範囲 $[e_i,e_n]$ 。

この範囲 $[e_l e_u]$ は,観測される信号線 $v_e$ が次の式で与えられる時,故障によって導かれるであろう電圧範囲。

$$v_{e} = \frac{e_{l} - e_{u}}{f_{l} - f_{u}} v_{f} + \frac{e_{l} f_{u} - e_{u} f_{l}}{f_{u} - f_{l}}$$

(1)

$(v_f:$  故障信号線における縮退した電圧)

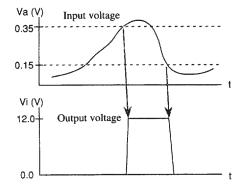

式(1)は,故障信号線と観測信号線の間のI/O関係が図に示すような線形関係で表される区間内に,その故障電圧範囲が含まれていること示している。

それぞれの信号線は、その信号線で検出可能な 故障を表わす故障表現を集めた一つの故障リスト を持つ。各素子に対する故障伝搬の操作は、その 入力における故障リストに対し、出力における故 障リストを次のように計算することで行われる。

- 1. 故障電圧範囲を重ならないように分割する。

- 2. 各故障に対して入力での電圧を計算する。

- 3. 各故障に対して出力での影響を計算する。

- 4. 各出力において検出可能な故障をピックアップする。

これらの計算の詳細を, Fig. 5に示すコンパレータの例を使用して説明する。

コンパレータに対する故障伝搬を示す。

p1, p2およびp3は, コンパレータ内の信号線とする。

Fig. 5 Comparator.

正しい電圧値:  $V_{in+} = 4$ ,  $V_{in-} = 3$ ,  $V_{out} = 5$

入力*in*+における故障リスト: (p1 [0.5 3] [2 4]), (p2 [2 4] [3.5 3]), (p2 [1 1.5] [3 1])

出力*in*-における故障リスト: (p2 [2 3] [0 0.5]), (p3 [1 2] [0 0.5]), (p2 [0 1.5] [0 2])

ここで各故障は,(故障信号線,故障電圧範囲, 影響電圧範囲)の形式で表現されるものとする。 このとき,出力OUTで検出可能な故障は次のよう な段階を経て計算される。

故障電圧範囲の分割:この操作では,同じ信号線で重なりを持った複数の故障電圧範囲を,各故障電圧範囲の重なりが生じないように分割する。

例えば,信号線p2で2つの故障(p2 [2 4] [3.5 3]) (p2 [2 3] [00.5])が与えられたとすると,これらはお互いに重なった部分を持っている。

そこでin+で検出可能な故障表現(p2 [2 4] [3.5 3]) は, (p2 [2 3][3.5 3.25])と (p2 [3 4] [3.25 3])の2つの 故障表現に分割される。同様に故障表現(p2 [0 1.5] [0 2])は, (p2 [0 1] [0 1.33])と (p2 [11.5] [1.33 2])に分割される。

回路素子の機能は区分線形な形で定義されているので,故障電圧範囲が分割された場合には影響電圧範囲も以下の式に従って再定義される。

$$\left[\frac{e_{l}-e_{u}}{f_{l}-f_{u}}f'_{l} + \frac{e_{l}f_{u}-e_{u}f_{l}}{f_{u}-f_{l}} \quad \frac{e_{l}-e_{u}}{f_{l}-f_{u}}f'_{u} + \frac{e_{l}f_{u}-e_{u}f_{l}}{f_{u}-f_{l}}\right]$$

(2)

ここで,分割前の故障表現は,(p [ $f_l f_u$ ] [ $e_l e_u$ ])であり,新しい電圧範囲は,[ $f'_l f'_u$ ]となる。

入力での影響の評価:各入力での故障の影響は, 各入力ごとのすべての故障表現から評価される。 それらは,故障伝搬表という形にリストされる。

与えられた故障リストに対して入力での故障伝搬表は, Table 5のようになる。

出力での影響の評価:評価される回路素子の機能 モデルに従って出力での電圧範囲が計算される。

出力での電圧は次のように計算される。まず, 故障電圧範囲は,故障信号線と出力の電圧の間に 線形関係が成り立つような小範囲に分割される。 そして,各小範囲に対して回路素子の機能に応じ て影響電圧範囲が計算される。

今回の例では,計算の結果はTable 5に示されるようになる。一つの故障電圧範囲は2つの小範囲に分割される;一つは $V_{in+} > V_{in-}$ が出力で $V_{out} = 5$ Vとなるものであり,もう一つは, $V_{in+} < V_{in-}$ が出力で $V_{out} = 0$ Vとなるものである。線形区間内の故障電圧範囲は分割される必要はない。

故障信号線 $_P1$ の故障電圧範囲の例 $[0.5\ 3]$ は, $[1.75\ 3]$ と $[0.5\ 1.75]$ の二つに分割される。故障電圧範囲 $[1.75\ 3]$ は, $V_{in+}>V_{in-}$ となり,もう一つの故障電圧範囲 $[0.5\ 1.75]$ では $V_{in+}< V_{in-}$ となる。

検出可能な故障のピックアップ:出力において故 障がある場合とない場合とで電圧値が異なるとき, その故障は検出可能である。

今回の例では,故障の影響電圧範囲が正常電圧とことなるときその故障は検出可能であると定義する。 Table 6によれば,故障表現(p1 [0.5 1.75] [0 0])および(p2 [1.3 1.5] [0 0])が出力outで検出可能である。

Table 5 Effect on fan-in pins.

| Faulty net | Faulty range | Effective range in+ | Effective range in- |

|------------|--------------|---------------------|---------------------|

| p1         | [0.5 3]      | [2 4]               | 3                   |

| p2         | [0 1]        | 4                   | [0 1.33]            |

| p2         | [1 1.5]      | [3 1]               | [1.33 2]            |

| p2         | [2 3]        | [3.5 3.25]          | [0 0.5]             |

| p2         | [3 4]        | [3.25 3]            | 3                   |

| p3         | [1 2]        | 4                   | [0 0.5]             |

Numbers not in parentheses present correct values.

### 3.2 実行例

回路例をFig. 6に示す。各回路素子 (b1: AMP, b2, b3:CMP, b4, b5:NOR, b6:ASW)の機能は, Table 7で与えられるものとする。この回路の入出力の電圧関係はFig. 7に示されるものとする。この回路はセンサからの明るさ入力に応じて自動車のヘッドライトの点灯を制御する機能を持つコンライト(conlight)回路である。

入力aが0.1Vにセットされ,信号線gが0.0Vに初期化されたとき,信号線dで[0.0~5.0]の電圧値の縮退故障が仮定される。

このときの故障の伝搬の様子をTable 8に示す。

- 信号線dにおいては,その影響電圧範囲は故障 電圧範囲に等しい。

- 信号線eにおいては,1.5V以上の故障電圧範囲が伝搬される(Table 9参照)。

- 信号線fにおいては,3.5V以上の故障電圧範囲が伝搬される(Table 10参照)。

- c 3.5V b2 f b4 h

b 1.5V b3 e b5 g b6 i

Fig. 6 An example of mixed-signal circuits.

Table 6 Effect on fan-out pin.

| Faulty net | Faulty range | Effective range in+ | Effective range in- | Effective range out |

|------------|--------------|---------------------|---------------------|---------------------|

| p1         | [1.75 3]     | [3 4]               | 3                   | 5                   |

| p1         | [0.5 1.75]   | [2 2.5]             | 3                   | [0 0]               |

| p2         | [0 1]        | 4                   | [0 1.33]            | 5                   |

| p2         | [1 1.3]      | [3 1.75]            | [1.33 1.75]         | 5                   |

| p2         | [1.3 1.5]    | [1.75 1]            | [1.75 2]            | [0 0]               |

| p2         | [2 3]        | [3.5 3.25]          | [0 0.5]             | 5                   |

| p2         | [3 4]        | [3.25 3]            | 3                   | 5                   |

| p3         | [1 2]        | 4                   | [0 0.5]             | 5                   |

|            |              |                     |                     |                     |

Numbers not in parentheses present correct values.

- 信号線gにおいては,最初の評価では故障電圧 範囲は伝搬されない(Table 11参照)。

- 信号線ħにおいては,最初の評価では3.5V以上の故障電圧範囲が伝搬される(Table 12参照)。

- 信号線gにおいては,第2回評価で3.5V以上の 故障電圧範囲が伝搬される(Table 13参照)。 信号線dにおける故障電圧範囲[3.5 5.0]によっ て伝搬された信号線gの影響電圧範囲は,信号

Fig. 7 The I/O relation of the example circuit.

Table 7 Functionality of blocks.

| AMP : Amplifier                                           |                             |  |  |  |  |

|-----------------------------------------------------------|-----------------------------|--|--|--|--|

| $V_{in} < 3V$ $-3V < V_{in} < 3V$ $V_{in} > 3V$ Otherwise | -30V                        |  |  |  |  |

| $-3V < V_{in} < 3V$                                       | $V_{in} \times 10 \text{V}$ |  |  |  |  |

| $V_{in} > 3V$                                             | 30V                         |  |  |  |  |

| Otherwise                                                 | Undefined                   |  |  |  |  |

| NOR: 2 inputs NOR                                      |           |  |  |  |  |

|--------------------------------------------------------|-----------|--|--|--|--|

| $V_a > 2V$ $V_b > 2V$ $V_a < 2V \text{ and } V_b < 2V$ | 0V        |  |  |  |  |

| $V_b > 2V$                                             | 0V        |  |  |  |  |

| $V_a < 2V$ and $V_b < 2V$                              | 5V        |  |  |  |  |

| Otherwise                                              |           |  |  |  |  |

|                                                        |           |  |  |  |  |

| ASW : Analog switch                                    |           |  |  |  |  |

| $V_{in} > 2V$                                          | 12V       |  |  |  |  |

| $V_{in} > 2V$ $V_{in} < 2V$ Otherwise                  | 0V        |  |  |  |  |

| Otherwise                                              | Undefined |  |  |  |  |

線fが5V固定のため,信号線hでは検出可能にならない。

信号線:に伝搬される故障は,(d [3.5 5.0] [12.0 12.0])となる。これは,信号線dにおいて,3.5Vと5.0Vの間に縮退した故障であれば信号線:において12Vに縮退する故障として検出可能であることを示す。

## 3.3 故障シミュレーションの結果

3.1節で述べたアルゴリズムに基づく故障シミュレータを使用してTable 14に示すような3つの回路に対して故障シミュレーションを行った。回路C1は、Fig. 6に示したコンライト回路である。回路C2はその構造上の理由から、約4分の1の信号線の故障はランダムパターンでは故障検出が難しい回路である。回路C3は内部にフィードバック回路を複数含むため、シミュレーションにおいてイベントを多く発生しシミュレータには負荷の高い回路で

Table 8 Transmission of faults in an example circuit.

| Signal line | Correct value | Detectable faults         |

|-------------|---------------|---------------------------|

| a           | 0.1           |                           |

| d           | 1.0           | (d [0.0 5.0] [0.0 5.0])   |

| e           | 5.0           | (d [1.5 5.0] [5.0 5.0])   |

| f           | 0.0           | (d [3.5 5.0] [5.0 5.0])   |

| h           | 5.0           | (d [3.5 5.0] [0.0 0.0])   |

| g           | 0.0           | (d [3.5 5.0] [5.0 5.0])   |

| i           | 0.0           | (d [3.5 5.0] [12.0 12.0]) |

Table 9 Fault propagation at block b3.

| Faulty net | Faulty range | b ( <i>in</i> +) | d (in-)   | e (out)       |

|------------|--------------|------------------|-----------|---------------|

| d          | [0.0 1.5]    | 1.5              | [0.0 1.5] | 5.0 (correct) |

| d          | [1.5 5.0]    | 1.5              | [1.5 5.0] | $[0.0 \ 0.0]$ |

Table 10 Fault propagation at block b2.

| Faulty net | Faulty range | d (in+)   | c ( <i>in</i> –) | f (out)       |

|------------|--------------|-----------|------------------|---------------|

| d          | [0.0 3.5]    | [0.0 3.5] | 3.5              | 0.0 (correct) |

| d          | [3.5 5.0]    | [3.5 5.0] | 3.5              | [5.0 5.0]     |

ある。回路C3はLSIへの適用を検討するために作成した回路である。

シミュレータはLucid Common Lispを使用して開発されている。シミュレーションはSun ELC (memory 64M byte)の上で実行された。

シミュレーションは次の条件のもとで実行された:

- 入力パターンは,各回路に対してアドホック (ad hoc)に作成され,回路に供給される。

- 各信号線においては,-30Vから30Vまでの故障電圧範囲が仮定される。

- 一旦検出可能となった故障は,後のシミュレーションからは除外される。

Table 15に,各シミュレーションにおける結果,実行時間,故障検出率,発生したイベント数を示す。故障検出率は,-30Vから30Vまでの仮定された故障電圧範囲に対して検出可能だった電圧範囲の割合を示す。検出率100%は全範囲の縮退故障が検出可能であったことを示す。

#### 4. 考察

### 4.1 他の故障モデルとの比較

最近,故障による定常電流値の増大をモニタすることで,CMOSの論理回路ばかりでなく,アナログ回路においても,かなりの故障が検出できることが報告されている¹°。しかし,バイポーラ回

Table 11 Fault propagation at block b5.

| Faulty net | Faulty range | h   | e         | g             |

|------------|--------------|-----|-----------|---------------|

| d          | [1.5 5.0]    | 5.0 | [0.0 0.0] | 0.0 (correct) |

Table 12 Fault propagation at block b4.

| Faulty net | Faulty range | g   | f         | h         |

|------------|--------------|-----|-----------|-----------|

| d          | [3.5 5.0]    | 0.0 | [5.0 5.0] | [0.0 0.0] |

Table 13 Second fault propagation at block b5.

| Faulty net | Faulty range | h         | e         | g             |

|------------|--------------|-----------|-----------|---------------|

| d          | [1.5 3.5]    | 5.0       | [0.0 0.0] | 0.0 (correct) |

| d          | [3.5 5.0]    | [0.0 0.0] | [0.0 0.0] | [5.0 5.0]     |

路では,バックグラウンドとなる定常電流のレベルが大きいため,シグナルとなる故障による電流値増加の検出は難しい。さらに集積化が進むと,バックグラウンドの定常電流の割合が高くなるため,故障による電流値増加を検出することは困難になると思われる。

これに対して,今回提案した電圧値の縮退故障という故障モデルは,外部出力での電圧測定のため,今後の技術進歩による集積回路の大規模化に対しても有効性を失わないと思われる。また,大規模化に対応したスキャン設計など各種の検査容易化設計技術との組み合せも容易であると考えられる。

# 4.2 故障シミュレーションの有効性

例題の故障シミュレーションをSPICEなどの回路シミュレータで行なうことを考える。1回のDC解析に必要な時間は,今回使用した計算機環境では,約10秒から1分程度である。検出可能な電圧値の縮退故障をチェックするためには,故障の個数と入力パターンの積の回数だけDC解析を行う必要がある。このため,全ての検出可能な故障に対して故障シミュレーションを行うには膨大な時間がかかる。

今回,開発した故障シミュレータは,同時に多くの故障を扱うことが可能である。またイベントドリブン方式をとるため,変化する機能ブロックのみ評価対象となり,回路全体を評価する必要がある回路シミュレーションに比べ,処理が高速に

Table 14 Circuits of test run.

| Circuit | # of blocks<br>(analog/digital) | # of events pattern<br>in input pattern |

|---------|---------------------------------|-----------------------------------------|

| C1*     | 4/2                             | 15                                      |

| C2      | 8/92                            | 45                                      |

| C3      | 4/64                            | 76                                      |

\*: C1 is a circuit shown in Fig. 7

Table 15 Results of test run.

| Circuit | Fault coverage at each line (%) | execution<br>time (sec) | # of total<br>events |

|---------|---------------------------------|-------------------------|----------------------|

| C1      | 95 - 100                        | 53.18                   | 203                  |

| C2      | 0 - 100                         | 5229.41                 | 10593                |

| C3      | 44.5 - 100                      | 24279.16                | 40548                |

行なえる。今回の例題の場合,回路シミュレータに基づく故障シミュレーションに比較して50倍以上高速である。

# 5. まとめと今後の課題

本論文ではアナ/ディジ混載IC用のテスト支援の ための新しい故障モデルと高速な故障シミュレー ションの手法を提案した。

- ・故障モデルとして、アナログ機能ブロックに電圧値の縮退故障を仮定する電圧値の縮退故障を仮定する電圧値の縮退故障というモデルを提案した。故障モデルの妥当性を検証するためにアナログ機能ブロックに対して故障解析を行った。それによれば、提案する故障モデルで内部に仮定したオープン/ショート故障の50%程度が出力端子で検出可能な故障として、カバーできることがわかった。提案する故障モデルでテストを行うことは十分な意味があると考えられる。

- ・この故障モデルを使用した新しい故障シミュレーションのアルゴリズムを提案した。この故障シミュレーションは、従来のディジタル回路に対する故障シミュレーションの拡張版となっている。試作した故障シミュレータは、回路シミュレータを流用した従来の故障シミュレーションに比べ50倍以上高速に実行可能である。

- ・上記の結果より,我々が提案する故障モデルと故障シミュレーション手法を用いることにより,アナ/ディジ混載ICのテストパターンの評価を適切にかつ高速に行うことができることが示された。

- 今後は、より大規模な回路に対して故障シミュレーションを行うこと、テストパターンの自動生成を検討することが課題である。

#### 謝辞

株式会社豊田中央研究所機械認識研究室原田義久室長と,同ソフトウェア研究室佐野範佳研究員には故障モデル検討に協力して頂いた。同回路設計研究室林宏明技師補には回路シミュレーションの実行で協力して頂いた。また,日本電装株式会社IC技術I部畑講平主任部員,瀬谷修担当部員には,有用性に関する議論と貴重な助言に感謝する。

# 参考文献

- Duhamel, P. and Roult, J. C.: "Automatic Test Generation Techniques for Analog Circuit and Systems: A Review", IEEE Trans. on CAS, 26-7(1979)

- Meixner, A. and Maly, W.: "Fault Modeling for the Testing of Mixed Integrated Circuits", Proc. Int. Test Conf., (1991), 564

- Walker, A., Alexander, W. E. and Lala, P. L.: "Fault Diagnosis in Analog Circuits Using Element Modulation", IEEE Design & Test of Computers, March(1992), 19

- Slamani, M. and Kaminska, B.: "Analog Circuit Fault Diagnosis Based on Sensitivity Computation and Functional Testing", IEEE Design & Test of Computers, March(1992)

- Memink, G. J., Meijer, B. W. and Kerkhoff, H. G.: "Testability Analysis of Analog Systems", IEEE Trans. on CAD, 9-6(1990)

- Souders, T. M. and Stenbakken, G. N.: "A Comprehensive Approach for Modeling and Testing Analog and Mixedsignal Devices", Proc. Int. Test Conf., (1990), 169

- Alani, A. F., Musgrave, G. and Ambler, A. P.: "A Steady-State Response Test Generation for Mixed-Signal Integrated Circuits", Proc. Int. Test Conf., (1992), 415

- Kao, et al.: "New Design for Testability Methods an Tools for Mixed Signal IC's", ATE & Instruction Conf., (1992), 153

- Pickel, P. F.: "Automated Development of Test Program Sets for Analog Circuit Modules", Symposium Proc. IEEE Int. Automatic Test Conf., (1988)

- 10) 三浦, 内藤, 樹下: "コンパレータの故障解析とテスト手法", 信学技報, VLD92-27, ICD92-167(1993)

- 11) Soclof, S.: Analog Integrated Circuits,(1985), 366, Prentice-Hall

- 12) Teshima, S., et al: "Very Fast Fault Simulation for Voltage Stuck-at Faults in Analog/Digital Mixed Circuit", IEICE Trans. on Inf. & Syst., E78-D, 7(1995), 853

# 著者紹介

中條直也 Naoya Chujo

生年:1958年。

所属:機械認識研究室。

分野:自動車用ECUの設計支援に関する

研究。

学会等:情報処理学会, IEEE Computer Soc.会員。

手嶋茂晴 Shigeharu Teshima

生年:1961年。

所属:ソフトウェア研究室。

分野:車載ECUのソフトウェア設計に関

する研究。

学会等:情報処理学会,電子情報通信学

会会員。